Et hittil forholdsvis ukjent selskap, Tilera, kunngjør i dag en 64-kjernet prosessor, Tile64, beregnet på spesialisert utstyr for å håndtere henholdsvis nettverkstrafikk og digital video. Tile64 beskrives som den første i en ny serie prosessorer med en «revolusjonerende arkitektur» som skal kunne skaleres til mange tusen kjerner.

Selv om hver kjerne omfatter en vanlig CPU, er det altså i første omgang ikke snakk om å bruke Tile64 til allmenne beregningsoppgaver, men til å prosessere nettverkstrafikk og video.

Selskapet tror de første praktiske anvendelsene vil komme innen for eksempel videokonferanser, automatisk prosessering av bilder fra utstyr for videoovervåking – som ansiktsgjenkjenning – og løpende analyse av nettverkstrafikk i sanntid for å sile ut ondsinnet kode.

Ifølge Tilera er Tile64s samlede ytelsen 10 ganger større enn en tokjernet Xeon, med en tredel av strømforbruket. Sammenliknet med den ledende DSP-en (en prosessor som håndterer digitale signaler) TMS320DM648 fra Texas Instruments, er ytelsen til Tile64 40 ganger så stor.

Foranledningen til Tile64er et forskningsprosjekt som startet ved MIT i 1996, ledet av Anant Agarwal som i dag er teknologidirektør i Tilera. Prosjektet ble finansiert gjennom flere millioner dollar fra det offentlige, dels National Science Foundation, dels USAs forsvarsdepartement gjennom Darpa. Hensikten var å realisere en prototyp på en prosessor bygget på en arkitektur utviklet av Agarwal, døpt «mesh-based multicore». Prosjektet ble kjent under navnet «Raw».

Prototypen ble realisert i 2002. To år etter ble Tilera etablert i det skjulte. Selskapet gjorde sin første offentlige opptraden i våres. Fagtidsskriftet EETimes ble så imponert at de utropte Tilera til en av årets 60 viktigste oppstarter.

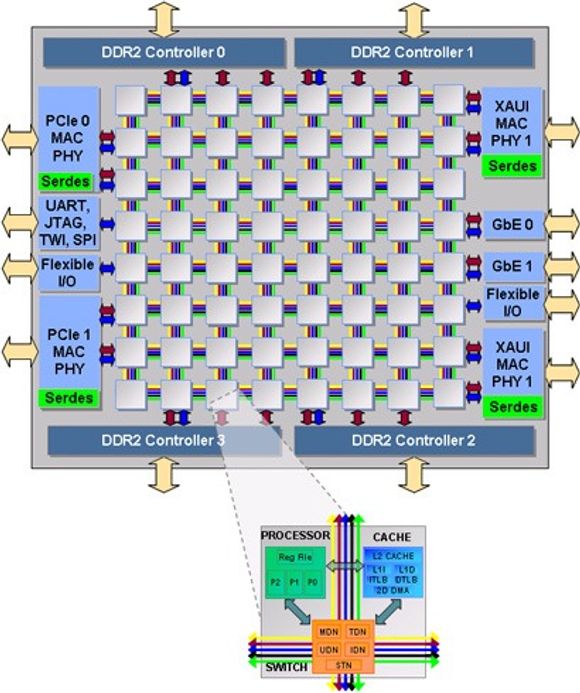

Navnene Tilera og Tile64 henspeiler på at kjernene legges ut som fliser (engelsk: «tile») på et gulv, uten annen tilkobling enn til de nærmeste flisene. Det er ingen sentral buss i prosessoren, bare det Tilera kaller «iMesh Interconnect». Blokk-diagrammet nedenfor til Tile64-prosessoren formidler hvordan dette fungerer:

Tilera mener iMesh er den viktigste nye utviklingen innen prosessorarkitektur de siste ti årene.

– Vi utviklet denne nye arkitekturen fordi eksisterende flerkjerneteknologier rett og slett ikke kan skalere utover en håndfull kjerner. Dessuten har våre kunder [en titalls kunder er allerede i ferd med å innlemme Tile64 i sine bokser] gjentatte ganger uttalt at dagens utviklingsverktøy for flerkjernede prosessorer er svært primitive, fordi de bygger på modeller hentet fra utvikling til énkjernede prosessorer. Vi innfører en revolusjonerende plattform for maskin- og programvare, der vi har løst de grunnleggende utfordringene med skalerbarhet innen flerkjernede prosessorer, forklarer Tilera-sjef Devesh Garg.

Tilera mener at buss-arkitekturen nødvendigvis lager trafikkork, siden all data må gjennom den samme banen. iMesh («intelligent mesh») derimot lager mange parallelle baner på kryss og tvers i hele prosessoren. Flere patenterte løsninger bidrar til å øke ytelsen og fleksibiliteten til denne ordningen, ifølge selskapet. Det innebærer at tallet på kjerner kan legges opp utfra hva brikken skal brukes til: Jo flere kjerner, dessto flere baner i iMesh-nettverket eller gitteret, og følgelig dessto større samlet båndbredde mellom kjernene, minne og I/O.

Hver kjerne i Tile64-prosessoren har evnen til å kjøre sitt eget operativsystem, for eksempel Linux. Hver kjerne har egen cache i nivå 1 og 2. Videre er det en distribuert nivå 3 cache. Som blokkdiagrammet ovenfor viser, er det videre fire DDR2 minnekontroller og en rekke høyhastighets I/O-grensesnitt. Det er også et programmert grensesnitt for å la prosessoren utveksle data med eksterne lagringsenheter.

Med Tile64 leverer Tilera utviklingsmiljøet MDE («Multicore Development Environment»). Det er et integrert miljø basert på Eclipse. Det omfatter en ANSI standard C-kompilator, en simuleringsmodell, flere kommandolinjegrensesnitt, grafiske verktøy for debugging og et applikasjonsbibliotek.

Foreløpig er Tile64 priset til 435 dollar, forutsatt innkjøp av minst 10.000 om gangen.

Tilera har varslet at de utvikler to nye prosessorer med den samme iMesh-arkitekturen, med henholdsvis 36 og 120 kjerner.

Tilera er ikke alene om å bruke mesh-prinsippet på flerkjernede prosessorer. Wall Street Journal siterer analytiker Will Strauss i Forward Concepts, som nevner to andre selskaper: Oregon-selskapet Ambric som utvikler en prosessor med 344 kjerner, og California-selskapet Stream Processors som utvikler en 80-kjernet prosessor.

En tredje konkurrent er Intel: Deres prosjekt Tera-scale dreier seg foreløpig om en allmentorientert prosessor med 80 kjerner.

Les også:

.jpg)

- [21.06.2011] Intel med virkelig mange kjerner

- [28.10.2009] Utfordrer Intel med 100-kjerners prosessor

- [09.11.2007] AMD med nytt kort for tunge regneoppgaver

- [12.02.2007] Intel viser 80-kjernet teraflops brikke

- [27.09.2006] Intel tester prosessor med 80 kjerner