På den internasjonale superdatakonferansen i Hamburg i går – International Supercomputing Conference – presenterte Intel sin nye arkitektur for framtidens superdatamaskiner, MIC for «Many Integrated Core».

Intel er allerede tungt engasjert i superdatamaskiner og «high performace computing» (HPC). Av den nye Top500-listen over verdens kraftigste tallknusere, som også ble lagt fram på konferansen i Hamburg, drives 82 prosent av Intel-prosessorer.

De siste årene har det vært en trend bort fra at tungregneanlegg bygges opp som klynger av rene industristandardprosessorer. I stedet har man satset på også å utnytte regnekraften i koprosessorer, særlig dem som vanligvis brukes til grafikkberegninger i pc-er og arbeidsstasjoner. Den kinesiske maskinen »Nebulae» som erobret andreplassen på Top500-listen, er for eksempel satt sammen av Intel Xeon-prosessorer og Nvidia grafikkprosessorer.

MIC-arkitekturen bygger på nettopp dette prinsippet: Superdatamaskinen bygges opp med klynger av Xeon-prosessorer utvidet med egne koprosessorer som akselererer beregningene.

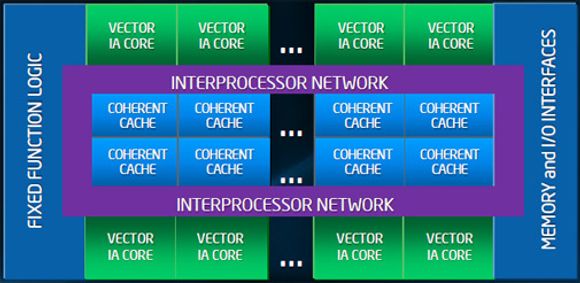

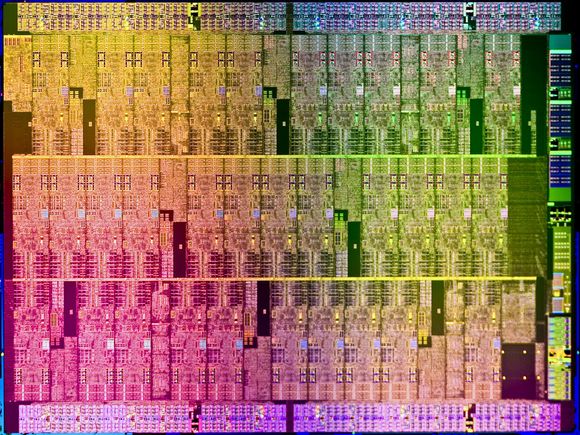

Den første HPC-koprosessoren i MIC-arkitekturen har fått kodenavnet «Knights Corner». Den vil produseres i en 22 nanometers prosess, og vil kunne skalere til over 50 kjerner på én brikke. Koprosessoren vil komme til sin rett i oppgaver der mange beregninger skal utføres parallelt, altså samtidig. Dette er typisk for vitenskapelige anvendelser og innen avanserte simuleringer.

Skjemaet som Pradeep Dubey, direktør for Intel Throughput Computing Lab, la fram i Hamburg, viser at «Knights Corner» i seg selg er en slags miniklynge på én brikke, der alle kjernene oppfører seg som en standard Intel-prosessor (IA står for «Intel Architecture»):

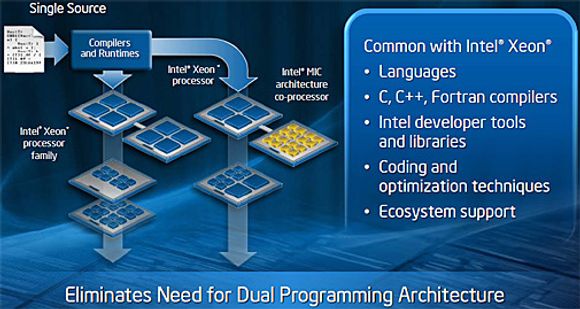

Å dele opp kompliserte beregninger opp i tråder som kan gjennomføres parallelt slik at alle kjerner utnyttes maksimalt, er en stor utfordring. Hittil har man løst dette ved det Intel kaller «dobbel programmeringsarkitektur»: Man tyr til ett sett med verktøy for å programmere til vanlige servere, og et annet sett for å programmere for tallknusende klynger som arbeider parallelt.

I MIC-arkitekturen tar Intel sikte på at utviklere kan anvende de samme verktøyene uansett om applikasjonen skal kjøres på vanlige Xeon-prosessorer, eller på Xeon supplert med MIC-koprosessorer.

Tilpasningen til parallell kjøring skjer ikke i kildekoden, men i kompilatoren eller i runtime. Løftet om felles programmeringsarkitektur for Xeon og for MIC ble uttrykt i denne plansjen fra Skaugens presentasjon:

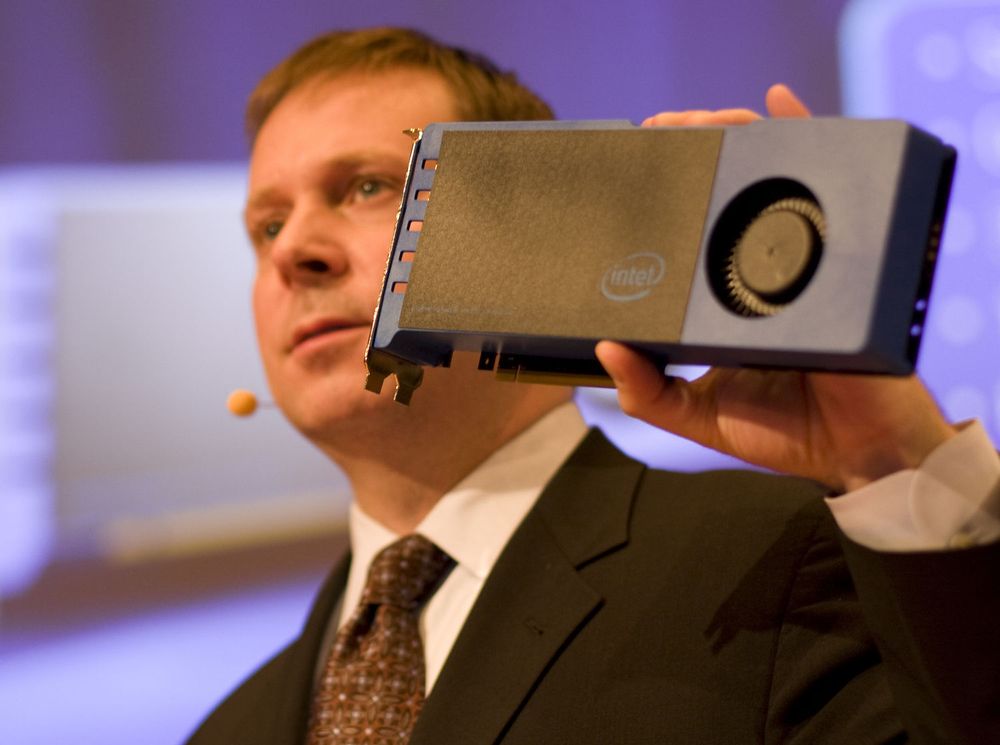

Intel har allerede begynt å tilby utviklerverktøy til MIC-arkitekturen. Den første pakken, døpt «Knights Ferry» er allerede tilgjengelig for spesielt utvalgte. I tillegg til programvareverktøy, omfatter den et utvidelseskort med en egen MIC-maskin. Knights Ferry ble presentert slik:

Blant de første til å prøve ut MIC og Intels nye hjelpemidler, er det europeiske senteret for kjerneforskning CERN. Sverre Jarp, teknologisjef i CERN Openlab, fortalte at de hadde bare brukt noen dager på å overføre et kompleks testprogram for parallelle beregninger, programmert i C++, til MIC-plattformen.

– MIC-plattformen har Intels kjente programmeringsmodell. Det var derfor vi kunne få programmet opp å kjøre langt raskere enn vi hadde ventet, sa Jarp fra podiet på konferansen.

Intel ser for seg at MIC vil kunne skaleres til exaflopsnivå.

De har kunngjort et samarbeid med det tyske forskningssenteret Forschungszentrum Jülich – som har Europas kraftigste superdatamaskin, basert på IBMs Blue Gene-teknologi med Power-prosessorer – og det tyske kompetansesenteret ParTec for å etablere et tungeregnelaboratorium i Jülich. Laboratoriet skal hete «ExaCluster Laboratory» (ECL). Samarbeidet skal pågå over mange år. Målet er å utvikle nye teknologier, verktøy og metoder for å skalere petaflopsmaskiner opptil og forbi exaflopsnivå, med vekt på skalerbarhet og feiltoleranse. ECL vil bli en del av Intel Labs Europe.

Les også:

- [19.06.2012] Snart kommer Intels 50-kjernede prosessor

- [25.06.2010] Intel scorer selvmål i sverteforsøk

- [01.06.2010] Lover petaflops-ytelse med ett eneste skap

- [31.05.2010] Kina nærmer seg superdata-toppen