Mye av utviklingen innen prosessorindustrien handler om å øke antallet kjerner i prosessorene. I tillegg til utfordringene med å få plass til flere kjerner i brikkene, samt å holde energiforbruket nede, må industrien også løse betydelige utfordringer knyttet til rask kommunikasjon mellom kjernene, systemminnet og I/O-systemene.

Mens AMD for lengst har satset på HyperTransport-teknologien, som er en toveis punkt-til-punkt-tilknytning med variabel bredde, er Intels systemer stadig basert på den klassiske, delte forsidebussen. Men nå ser det ut til at selskapet begynner å komme på andre tanker.

Under VLSI Symposium som arrangeres i Japan denne uken, vil selskapet legge fram dokumenter som blant annet beskriver en ny laveffekts brikke-til-brikke-forbindelse med støtte for datarater på inntil 15 gigabits per sekund, i tillegg til beskrivelse av teknikker for mer effektivt å spre oppgaver på tvers av flere kjerner og deres respektive minner. Det er dog ikke kjent når teknologiene vil tas i bruk i kommersielle produkter.

- Etter hvert er vi nødt til å greie å levere flere terabits i sekundet med data til en flerkjernet brikke. Men ved å bruke dagens teknikker vil det kunne kreve et effektnivå på hele 100 watt, sier Randy Mooney, direktør for Intel I/O-forskning, til EE Times.

Les også:

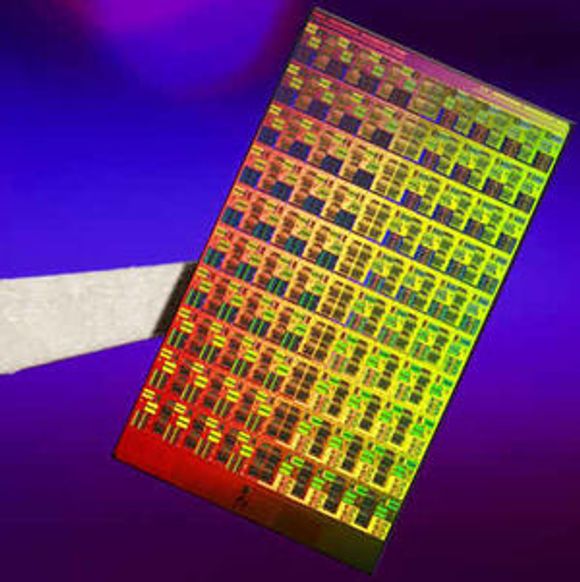

- [12.02.2007] Intel viser 80-kjernet teraflops brikke

- [27.09.2006] Intel tester prosessor med 80 kjerner

Under foredraget " A Scalable 5-15Gbps, 14-75mW Low Power I/O Transceiver in 65nm CMOS", som blant annet Mooney fortelle om en brikke-til-brikke-forbindelse som skalerer fra 5 til 15 Gbit/s per I/O-kanal med effektnivå på så lite som 2,7 mW per Gbit/s. Teknologien, som allerede er tatt i bruk i Intels 80-kjernet prosessor-prototyp som selskapet utviklet i fjor, skal ha et energiforbruk på mellom 14 og 75 milliwatt.

- Vi genererer rask I/O med så lite som 14 prosent av effekten som brukes i grensesnitt som er i produksjon i dag, hevder Mooney.

Ifølge EE Times har Intel oppnådd dette ved å ta i bruk flere ulike teknikker. Designet skalerer frekvensen og spenningsnivåene til både sender- og mottakerbrikkene. I tillegg har Intel brukt en passiv induksjonsspole i stedet for en motstand for å terminere datalinjene.

Brikken skal også redusere effektbehovet ved å eliminere klokkebuffere. Dette fører til variasjon i klokkeinformasjonen, men uten å få prosesseringsjobbene til å bryte sammen.

I dokumentet "A 5.1GHz 0.34mm2 Router for Network-on-Chip Applications" gir Intel mer detaljer om kjerne-til-kjerne-ruteren i den 80-kjernede prosessoren. Denne ikke-blokkerende ruteren støtter klokkehastigheter på over 5 GHz, en mesokron forbindelse som tillater modulbasert klokking, strømstyringskretser, en båndbredde på mer enn 100 gigabytes per sekund per node og en samlet båndbredde i brikken på minst 2,6 terabits/s.