I sin berømte artikkel i en utgave av magasinet Electronics som ble utgitt 19. april 1965, kom Gordon Moore – som senere ble toppsjef Intel – med flere forutsigelser. Den kjente, som kalles for Moores lov, spår at antallet transistorer i en integrert krets vil dobles hver andre år.

Mindre kjent er en spådom om oppbygningen av prosessorbrikker:

– Det kan vise seg å være mer økonomisk å bygge store systemer fra mindre funksjoner, som er separat pakket og sammenkoblet.

Slik avslører du skjult kamera med mobilen

Felles grensesnitt for chiplets

Dette ser vi i dag i flere moderne prosessorer, som består av flere separate silisiumbrikker som er koblet sammen, innenfor samme pakke. Disse brikkene kalles gjerne for chiplets.

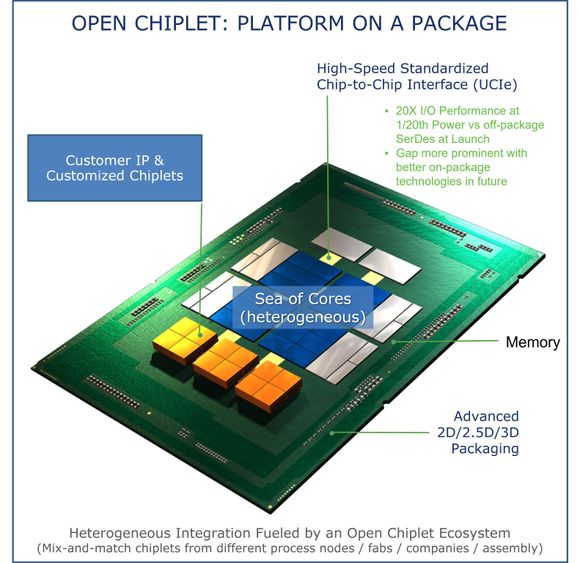

Nå har noen av verdens største teknologiselskaper, inkludert flere av de ledende prosessorleverandørene, stilt seg bak en ny standard for hvordan slike chiplets enklere kan kobles sammen på pakkenivå. Spesifikasjonen, som kalles for UCIe 1.0 (Universal Chiplet Interconnect Express), inkluderer både det fysiske laget, en protokollstakk, en programvaremodell og samsvarstesting.

Hensikten er å skape et helt økosystem for chiplets fra ulike leverandører.

Tunge aktører med fra starten

Spesifikasjonen er utgitt av en allianse som også heter Universal Chiplet Interconnect Express. Alliansen består per i dag av Advanced Semiconductor Engineering (ASE), AMD, Arm, Google Cloud, Intel, Meta, Microsoft, Qualcomm, Samsung og TSMC (Taiwan Semiconductor

Manufacturing Company).

UCIe trekker i dette dokumentet fram en del av fordelene med å bruke chiplets. Blant annet er det en grense hvor store hver silisiumbrikke kan lages. Dette henger sammen med det som kalles for «die reticle limit», som ifølge Semiconductor Engineering er den største brikkeoverflaten som kan eksponeres av litografiutstyr ved å bruke én enkelt maske uten at det oppstår feil forårsaket av forstyrrelser eller ufullkommenheter i masken.

Mer fleksibilitet

Mange av dagens prosessorer krever bruk av større silisiumbrikker, blant annet på grunn av antallet kjerner de skal leveres med. Antallet kjerner kan da bli begrenset av den nevnte grensen. Dette kan løses ved å fordele kjernene på to eller flere effektivt sammenkoblede chiplets.

En annen fordel med chiplets er at man lage ulike deler av prosessoren med forskjellige prosessteknologier. For eksempel kan man produsere prosessorkjernene med den nyeste prosessteknologien, mens man gjenbruker designen til I/O- og minnedelen fra en eldre generasjon av prosessoren. Dette kan gi lavere kostnader og kortere produktutviklingstid.

Det nevnte dokumentet gir også en nærmere beskrivelse av teknologiene. Selve UCIe 1.0-spesifikasjonen er bare tilgjengelig for medlemmene av alliansen. Det skal åpnes for flere medlemmer senere i år.

Reduser sløsingen med konsulenter!